# Homework 4

(Due date: March 26th @ 5:30 pm)

Presentation and clarity are very important! Show your procedure!

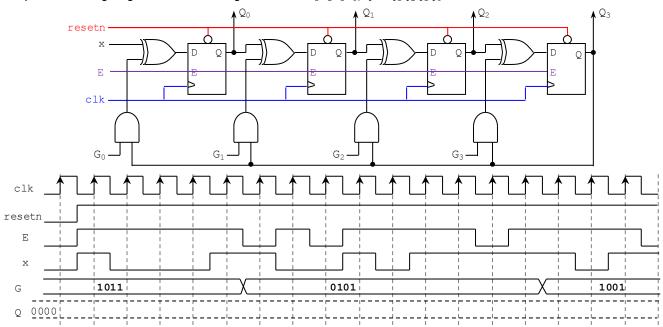

## PROBLEM 1 (14 PTS)

• Complete the timing diagram of the following circuit.  $G = G_3 G_2 G_1 G_0$ ,  $Q = Q_3 Q_2 Q_1 Q_0$

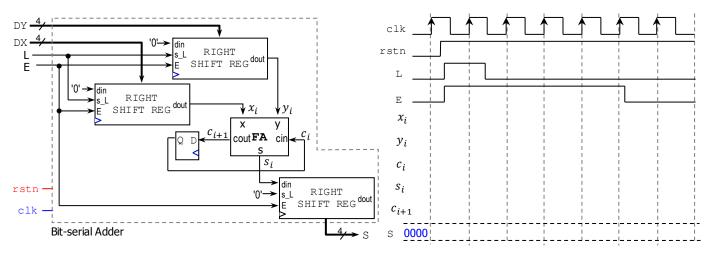

## PROBLEM 2 (18 PTS)

• Complete the timing diagram of the following bit-serial adder. DX=0101, DY=1001. (8 pts)

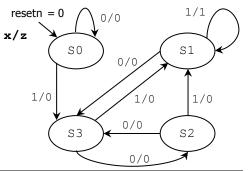

- Given the following State Machine Diagram (10 pts).

- ✓ Is this a Mealy or Moore Machine? Why?

- ✓ Get the excitation equations and the Boolean equation for z. (6 pts) Use S0 (Q=00), S1 (Q=01), S2 (Q=10), S4 (Q=11) to encode the states.

- $\checkmark$  Sketch the circuit for this Finite State Machine. (3 pts)

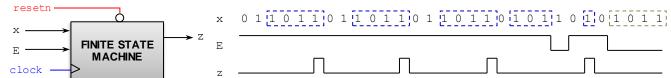

#### PROBLEM 3 (21 PTS)

- Sequence detector: The machine generates z = 1 when it detects the sequence 1011. Once the sequence is detected, the circuit looks for a new sequence.

- The signal *E* is an input enable: It validates the input *x*, i.e., if E = 1, *x* is valid, otherwise *x* is not valid.

- Draw the State Diagram (any representation), State Table, and the Excitation Table of this circuit. (14 pts)

- Provide the excitation equations and the Boolean equation for z (simplify your circuit: K-maps or Quine-McCluskey) (4 pts)

Sketch the circuit. Is this a Mealy or a Moore machine? Why? (3 pts)

- Sketch the circuit. Is this a Mealy or a Moore machine? Why? (3 pts)

## PROBLEM 4 (15 PTS)

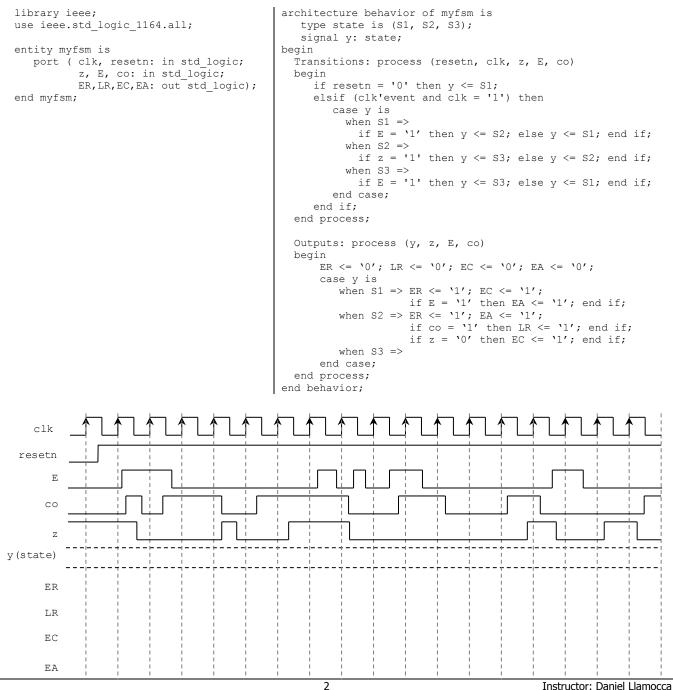

- Draw the State Diagram (in ASM form) of the FSM whose VHDL description in shown below. Is it a <u>Mealy or a Moore FSM</u>?

- Complete the Timing Diagram.

### PROBLEM 5 (17 PTS)

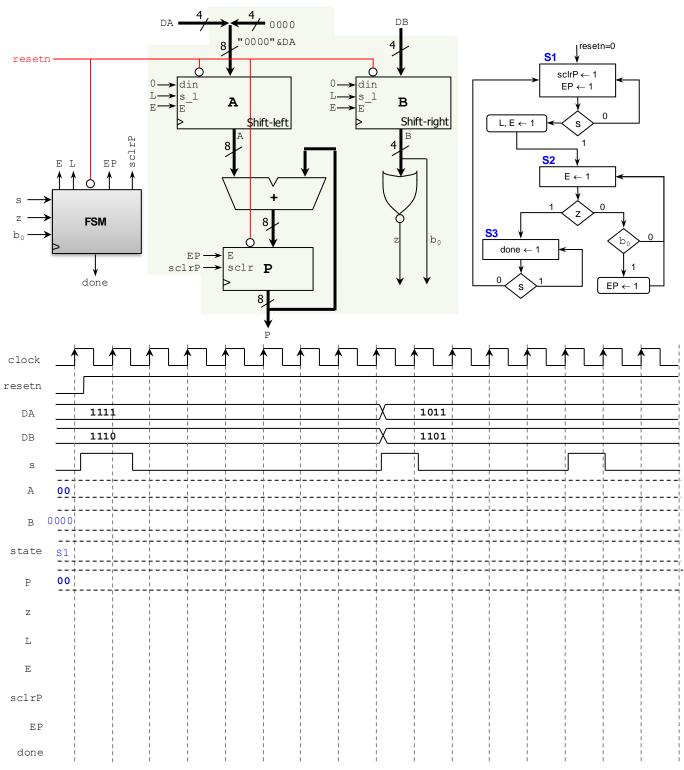

- Complete the following timing diagram (A and P are specified as hexadecimals) of the following Iterative unsigned multiplier. The circuit includes an FSM (in ASM form) and a datapath circuit.

- Register (for P): *sclr*: synchronous clear. Here, if *sclr* = E = 1, the register contents are initialized to 0. Parallel access shift registers (for A and B): If E = 1:  $s_l = 1 \rightarrow \text{Load}$ ,  $s_l = 0 \rightarrow \text{Shift}$

## PROBLEM 6 (15 PTS)

Attach a printout of your Project Status Report (no more than a page). This report should contain the current status of the project, including a block diagram of your system. You <u>MUST</u> use the provided template (Final Project - Report Template.docx).